WITH “BIG CHIP,” CHINA LAYS OUT ASPIRATIONS FOR WAFERSCALE

原文探討了中國科學院提出的一種他們稱為“Big Chip”的 Silicon Chiplet 晶片架構設計

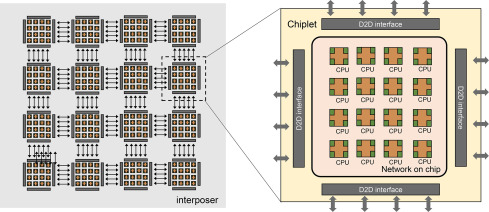

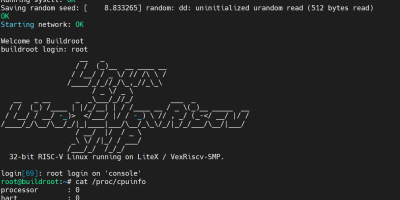

這顆是實驗性質的晶片,它將 16 顆 16 核的 RISC-V CPU 封裝在同一顆 CPU 內

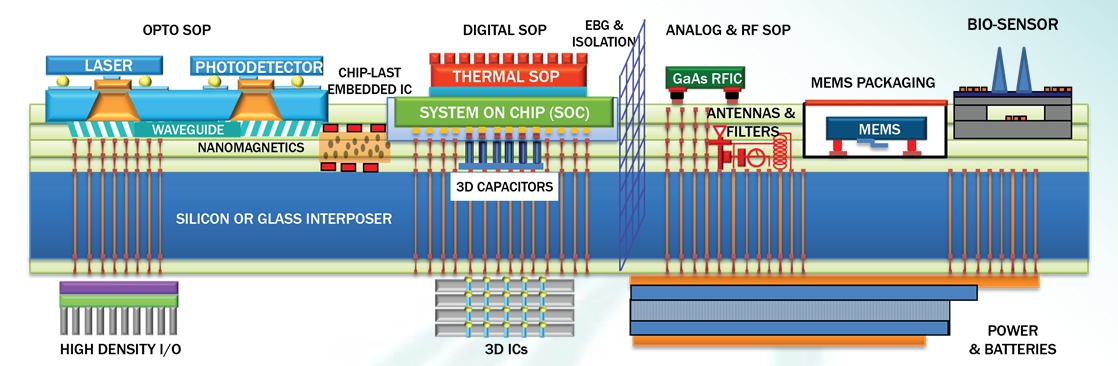

文內並且猜測這是使用 2.5D interposer interconnect 的技術,這是 SMIC 可以做到的,原 IC 是 22nm 製程,成熟製程,穩定度也比較好。我順手查了一下 2.5D interposer interconnect,一般不會這麼複雜,這只是示意圖,意思是所有的 IC 都放在一個矽或是玻璃基板上,再彼此互連

文章並沒有提到太多,但是畢竟是論文,而且開放直接存取(好評)。論文位置,The Big Chip: Challenge, Model and Architecture

上面的圖就很好的說明該 CPU 的架構,由 16 個 16 cores RISC-V 組合而成,透過 network on chip (NOC) 一般都是某種 BUS 互連。CPU 是 uniform design ,也就是一般使用上並不會有什麼差別

跟一般 chiplet 的差別是,像 Apple M 系列的晶片是二顆疊在一起,並不是透過 2.D 以外,一般做 chiplet 的通常是不同功能的疊在一起,像是華為就是 CPU + AI + IO (含 RF) 疊在一起。像 Nvidia 就是將 GPU 和 HBM(High Bandwidth Memory) 疊在一起,而這顆是將很多顆同功能的疊在一起。目前沒有做是因為沒有主要的商業價值,最大的價值還是突破美國技術封鎖的企圖心。

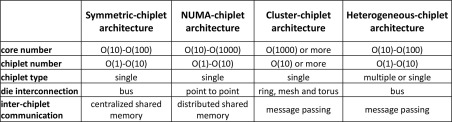

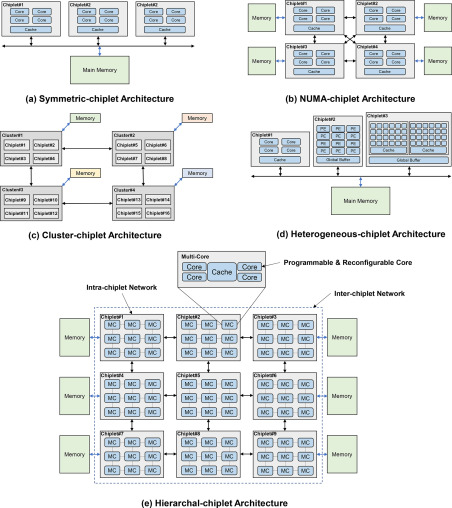

論文也給出了一般架構的比較,這次他們的 BIG CHIP 叫 Hierarchal chiplet architecture (註:看起來就好論文呀,都發明一些新名詞)

Symmetric-chiplet 就一般 CPU 數量比較少的會用,NUMA-chiplet 通常是 Server 等級的 CPU 會使用的架構,Intel CPU 互連部份比較像 Cluster-chiplet architecture

這顆 CPU 會出現最大的原因是他們要突破目前美國禁售 EUV 限制,因為如果沒辦法降低製程,增加 CPU 密度;才需要提前實作像這類的多顆多核CPU互連的 chiplet 架構,可以在現有的框架下,減少一些限制

這個有趣的想法,這個架構就只是一般的學術拿來做研究的,做出晶片只是第一步,後面的軟體地雷才多。如果他們眼光夠遠,這應該是整個計劃的第一部份,第二部份之後是研究這個架構的能問題,尤其是 CPU 互連,跨 CPU IO / Memory 或像是 CPU scheduling 等等問題,這些都是麻煩的部份,效能永遠是這種架構的核心問題

光是這架構的軟體部份應該可以寫出不少論文

不過這架構除了 Symmetric 可以玩,如果有效能問題還頗適合玩 asymmetric 架構的,還可以當 chip 內備援系統,非常適合車用呢。

發佈留言