大部份的環境都要用上一篇(Build Risc-V on Ubuntu Linux)相同的環境,但是其實還有更多的問題,中間也踩了不少地雷,還好都不算難解的問題

Table of Contents

Lattice Versa EVB Board 晶片型號不同

這個是最主要的問題,因為文件並不會提到這件事,都會用 versa_ecp5 帶過,但是實際上 versa_ecp5 是使用 LFE5UM5G-85F 的晶片,晶片比較新,邏輯閘數也比較多。一般市面上賣的 versa_ecp5 是 LFE5UM5G-45F,一片約在一萬元左右。

我從淘寶看到一塊比較便宜的 LFE5UM5G-45F ,結果買回來後是 LFE5UM-45F ,沒有 5G。查詢網路上的資料,大概只差在 SEDERS 最高頻可以到 5G ,還有速度比較快。

但是 LiteX default versa_ecp5 是預設用 LFE5UM5G-85F ,在燒錄時就會失敗,ID 不一樣

此時我們就要重編一次 Linux-on-litex-vexriscv ,加上 device 的參數,這樣就可以了

./make.py --device LFE5UM --board=versa_ecp5 --cpu-count=1 --build編出來的 bitstream 和 fpga hardware 不同的錯誤訊息,可以看到 hardware id 不一樣

$ openFPGALoader -b ecp5_evn versa_ecp5.bit

empty

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Open file: DONE

b3bdffff

Parse file: DONE

mismatch between target's idcode and bitstream idcode

bitstream has 0x81112043 hardware requires 0x01112043

Error: Failed to program FPGA: std::exception

連接上 EVB Board

EVB Board 應該支援 ethernet load ,但是我還沒試出來,就當 TBD 吧,看設定檔內 ethernet 是可以用的

EVB Board 上的 FT2232H 支援 JTAG 和 Serial Port ,Linux kernel 的 image 可以從 serial port load,不過速度好慢啊

我之前用 Diamond programmer 要燒錄編出來的 bitstream file ,但是因為 id mismatch 的關係所以燒不上去,所以我最後是找了一台乾淨的 Linux 直接接 EVB Board 的 USB (要注意,這塊版子的 USB Port 是 mini-USB ,如果沒附線要有支援 mini-USB 的線),就這樣找到最後才發現根本型號不一樣,所以這篇就不會提到 Diamond programmer

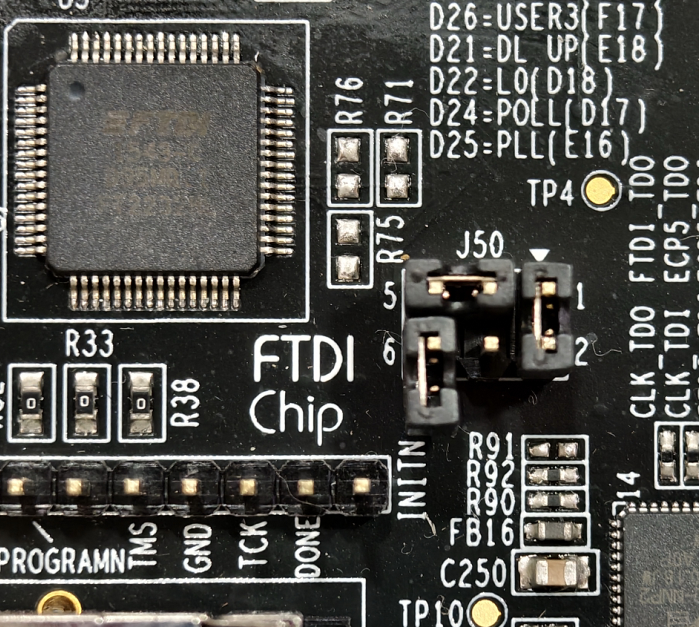

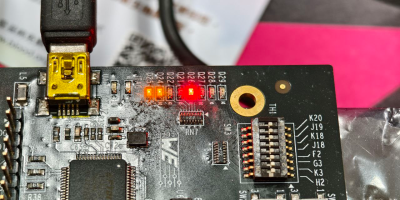

記得接上之前要將 FTDI 的J50跳線改成下圖這樣,要跳過 iSPclock

(原文 Note: If you are using a Versa board, you will need to change J50 to bypass the iSPclock. Re-arrange the jumpers to connect pins 1-2 and 3-5 (leaving one jumper spare). See p19 of the Versa Board user guide.)

接上去之後,上電之後,Linux 下會出現 /dev/ttyUSB0 是 JTAG 的介面,/dev/ttyUSB1 是 serial port 的介面

在另一個視窗先執行 litex_term(記得在 venv 環境下執行)

litex_term --images=images/boot.json /dev/ttyUSB1燒錄 bitstream 到板子上

最後一步就是燒錄上去了,我是用 OpenFPGAloader ,以下是安裝步驟

sudo apt install -y libftdi1-dev

cd /nvme/cpu

git clone https://github.com/trabucayre/openFPGALoader

cd openFPGALoader

mkdir -p build

cd build

cmake ../

make -j `nproc`

sudo make install 然後到 linux-on-litex-vexriscv 下用 OpenFPGAloader 暫時 load bitstream 上去,這速度很快,這樣就不用燒上去了

cd /nvme/cpu/linux-on-litex-vexriscv/build/versa_ecp5/gateware

$ openFPGALoader -b ecp5_evn versa_ecp5.bit

empty

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Open file: DONE

b3bdffff

Parse file: DONE

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.00%

Done

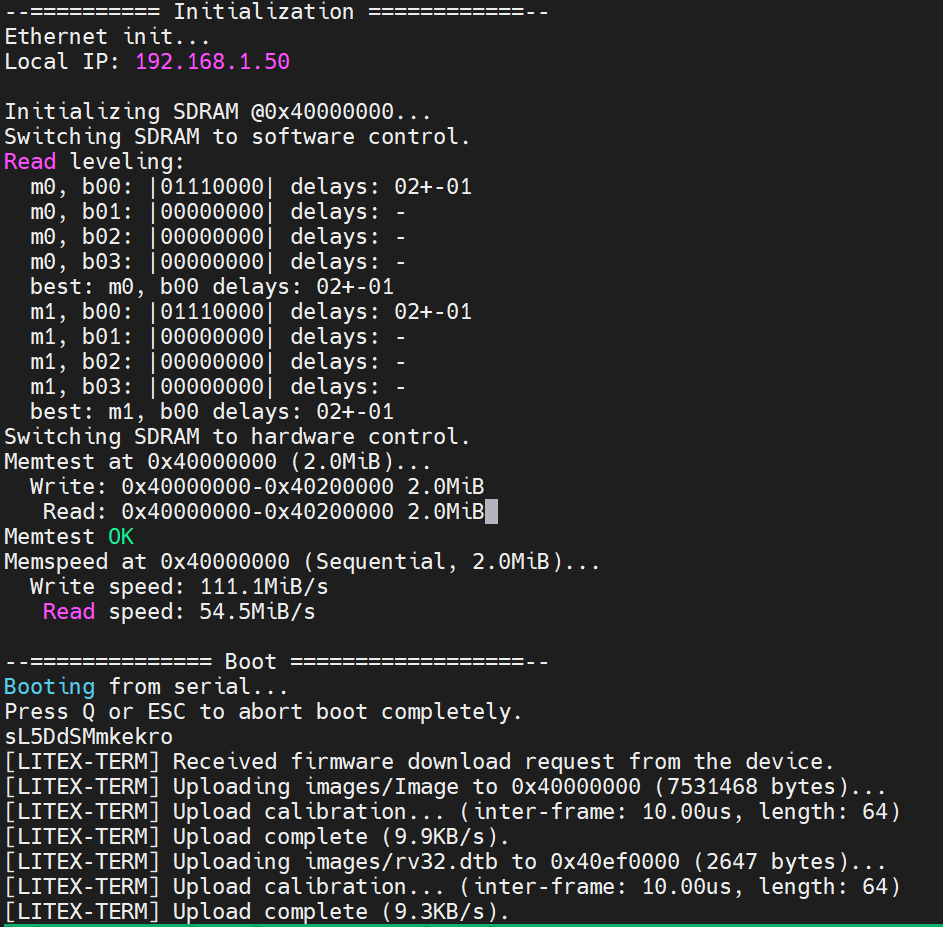

Disable configuration: DONE如果順利,可以在剛剛執行 litex_term 上看到 load image 訊息

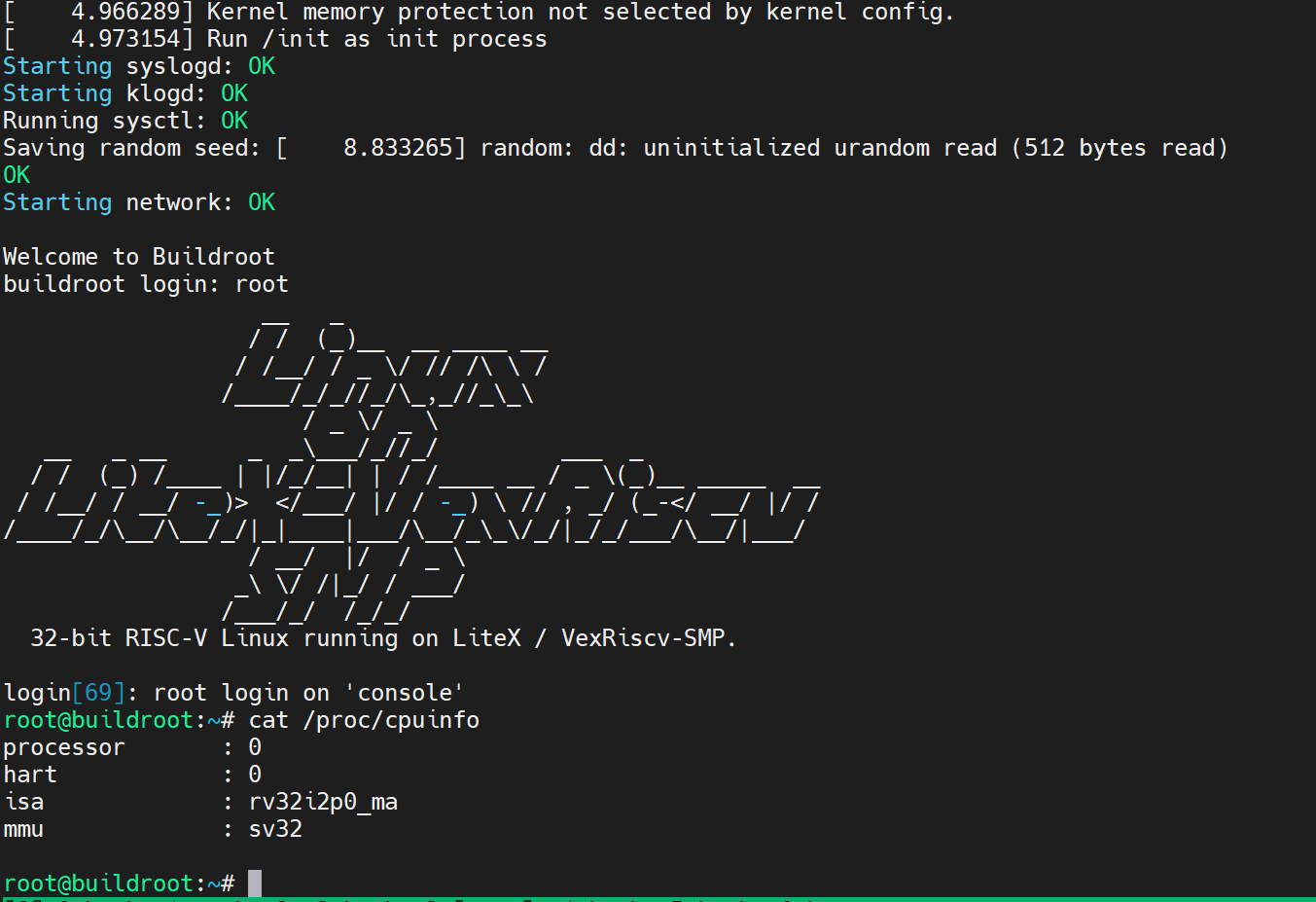

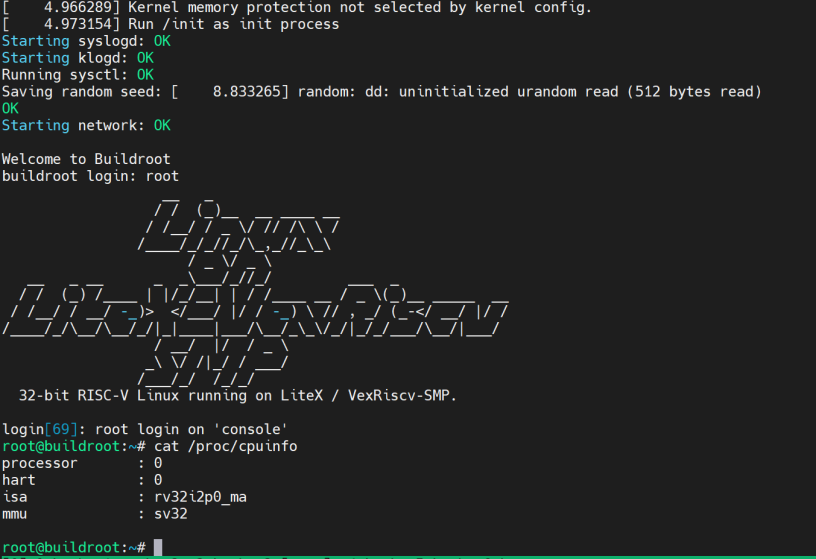

如果用的是上一篇文章內提到的先下載好 RiscV 的 Linux image 和 rootfs ,就可以看到 Linux boot 了

這年代可以自己編一顆 CPU 跑起來也真的是很有趣

以下未完成,待續

設定 udev

這塊版子看起來要設定過 udev 才能被 LiteX 抓到,首先新增檔案 /etc/udev/rules.d/99-ftdi.rules

內容如下,記得 GROUP=換成 Linux login 帳號

SUBSYSTEMS=="usb", ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", MODE="0660", GROUP="使用者名稱"

然後執行以下命令之後再重新上電即可

sudo udevadm control --reload-rules

sudo udevadm trigger這個命令也可以像 OpenFPGAloader 一樣將 bitstream load 到 FPGA 上

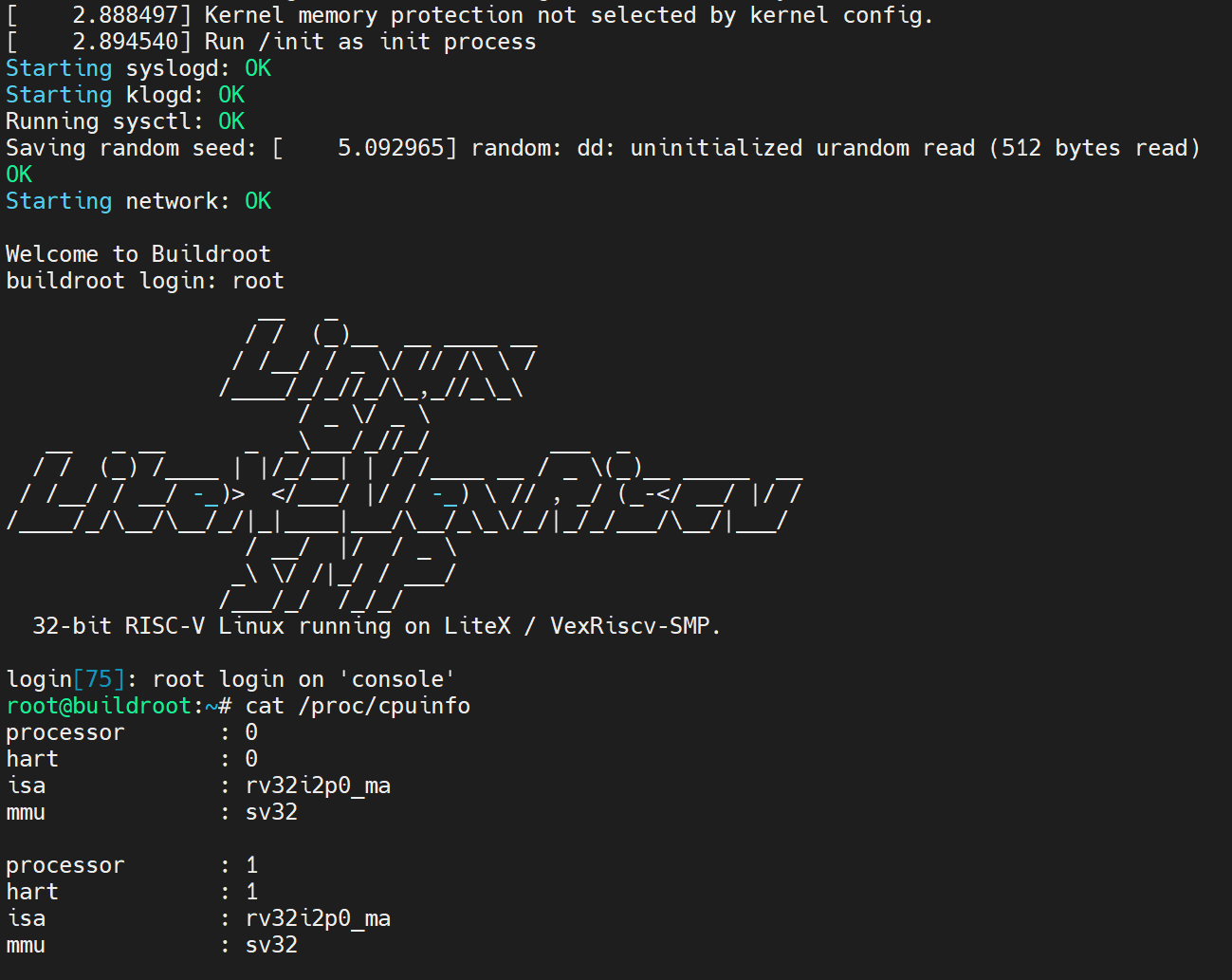

./make.py --device LFE5UM --board=versa_ecp5 --cpu-count=1 --load 45F Gate count 夠放二顆 CPU ,所以可以跑 SMP

./make.py --device LFE5UM --board=versa_ecp5 --cpu-count=2 --build

./make.py --device LFE5UM --board=versa_ecp5 --cpu-count=2 --load

發佈留言